# Nano-Micro Letters

# **REVIEW**

https://doi.org/10.1007/s40820-025-01769-2

Cite as Nano-Micro Lett. (2025) 17:255

Received: 7 February 2025 Accepted: 15 April 2025 © The Author(s) 2025

# **Two-Dimensional Materials, the Ultimate Solution for Future Electronics and Very-Large-Scale Integrated Circuits**

Laixiang Qin<sup>1,2</sup> , Li Wang<sup>1,2</sup>

# HIGHLIGHTS

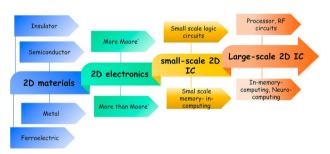

- With the incessant down-scaling of electronics, traditional semiconductors like Si are encountered with insurmountable hurdles to maintain performance increase without bringing about additional issues of power consumption escalating, in this context, twodimensional (2D) materials emerge as superior candidates to supersede or complement Si attributed to their marvelous electronic properties to further sustain the Moore's law life.

- 2D materials-based electronics in More Moore and More than Moore' regimes have attained promising achievements and showcased monumental potentials applications in low power consumption integrated circuits

- 2D materials-based integrated circuits have gone through a promising development, evolving from small-scale integrated circuits (ICs) to full-functioned processors. Whereas enormous endeavors are waited to be dedicated to realize large-scale ICs attributed to lack of large-scale 2D materials of electronic qualities and immature fabricating techniques.

**ABSTRACT** The relentless down-scaling of electronics grands the modern integrated circuits (ICs) with the high speed, low power dissipation and low cost, fulfilling diverse demands of modern life. Whereas, with the semiconductor industry entering into sub-10 nm technology nodes, degrading device performance and increasing power consumption give rise to insurmountable roadblocks confronted by modern ICs that need to be conquered to sustain the Moore law's life. Bulk semiconductors like prevalent Si are plagued by seriously degraded carrier

mobility as thickness thinning down to sub-5 nm, which is imperative to maintain sufficient gate electrostatic controllability to combat the increasingly degraded short channel effects. Nowadays, the emergence of two-dimensional (2D) materials opens up new gateway to eschew the hurdles laid in front of the scaling trend of modern IC, mainly ascribed to their ultimately atomic thickness, capability to maintain carrier mobility with thickness thinning down, dangling-bonds free surface, wide bandgaps tunability and feasibility to constitute diverse heterostructures. Blossoming breakthroughs in discrete electronic device, such as contact engineering, dielectric integration and vigorous channel-length scaling, or large circuits arrays, as boosted yields, improved variations and full-functioned processor fabrication, based on 2D materials have been achieved nowadays, facilitating 2D materials to step under the spotlight of IC industry to be treated as the most potential future successor or complementary counterpart of incumbent Si to further sustain the down-scaling of modern IC.

KEYWORDS 2D materials; Short channel effects; Integrated circuits; Degraded carrier mobility; Moore's law

Laixiang Qin, lxq@idt.eitech.edu.cn; Li Wang, liwang@eitech.edu.cn

<sup>&</sup>lt;sup>1</sup> Ningbo Institute of Digital Twin, Eastern Institute of Technology, Ningbo City 315100, Zhejiang, People's Republic of China

<sup>&</sup>lt;sup>2</sup> Eastern Institute of Technology, Ningbo City 315100, Zhejiang, People's Republic of China

#### **1** Introduction

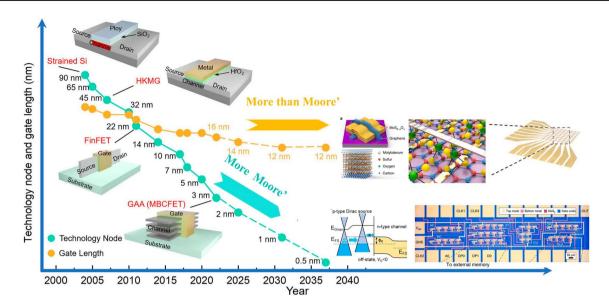

Since Gordern Moore proposed his famous Moore's law in 1965 [1], integrated circuits doubled every two years, manifesting by physical dimensions of discrete electronic device reducing by 0.7 times, ascribed to which the footprint reduces by  $\sim 0.5$  times. On the contrary, operating speed doubles, power dissipation and cost both decrement by a factor of two [2, 3]. The Moore's law had been complied with integrated circuits (ICs) happily during the former several decades until semiconductor industry entered into sub-100 nm node, where gate began to give over part of its electrostatic dominance over channel to drain bias attributed to drain's stealing behavior over channel barrier [4, 5]. In this context, the notorious short channel effects (SCEs) began to come into view and draw themselves enormous attention to be dedicated efforts to [6]. The prominent SCEs that seriously degrade device performance comprise of subthreshold swing (SS), drain-induced barrier lower (DIBL), punch-through, Subthreshold-voltage  $(V_t)$  rolling off in accordance with channel length scaling and leakage current increasing [7-10]. SS describes the switching capability of the device and the smaller the SS, the stronger the gate electrostatic control over channel is, and DIBL is on behalf of the competing behavior of drain bias over the controllability of channel with regards to gate bias. Punch-through denotes the phenomenon of the depletion region induced by source and drain doping jointing with each other under the channel region, contributing to leakage current increment, while  $V_t$  rolling off contributes to leakage current escalating and stability issue in circuits, where leakage current increasing finally results in static power consumption surging. The relentless downscaling of electronics poses imperative requests for novel device structures or ingenious materials which can reach a tradeoff between high discrete device performance and low power dissipation to sustain the Moore's law life further, this regime of semiconductor technology is termed as More Moore. For another, modern life brings forwards the requirements for 5G or 6G communication, cloud computing, artificial intelligent and neuromorphic computing, which all comes following the blossoming of More than Moore's regime [11]. More than Moore describes the integrated circuits boost their performance by incorporating of diverse kinds of electronics or optimizing the algorithm to achieve various and enhanced functions [12, 13].

2D materials have spawned dramatic interests ever since graphene was exfoliated in 2004 [14], and are treated as most potential candidates to supersede or complement bulk Si in the foreseeable future in semiconductor industry, which mainly originate from their remarkable electronic properties [15–17]. 2D materials possesses high carrier mobility maintainability regardless of thickness thinned down to sub-1 nm attributing to dangling bonds free and atomic smooth surface, which has long been plaguing bulk semiconductors whose carrier mobility seriously degrades proportionally to the six power of thickness ( $\sim t^6$ ) when thickness decreases to sub-5 nm regime [18]. Nevertheless, it is imperative for channel thickness to thin down proportionally in accordance with channel length to maintain sufficient gate controllability over channel to suppress SCEs according to Dennard's law [19], thus it seems impossible for bulk semiconductors exclusively to sustain downscaling to keep Moore's law alive in the coming future. New materials that act as successors or complementary counterparts are indispensable to further push the semiconductor technology nodes forward. 2D materials with atomic thickness, tunable bandgap, large effective mass that are capable of suppressing leakage current and compatibility with both front end of line (FEOL) and back end of line (BEOL) of Si production line come just at the right time, like destined in the fate [20, 21].

2D materials belong to a big family which possess a wide range of electronic properties, covering from insulators (hexagonal boron nitride (h-BN), Bi<sub>2</sub>SeO<sub>5</sub>, SrTiO<sub>3</sub>) [22-24], semiconductors (transition metal dichalcogenides (TMDCs) family) [25, 26], metal (graphene) [27] to ferroelectric materials (In<sub>2</sub>Se<sub>3</sub>, CuInP<sub>2</sub>S<sub>6</sub>) [28], fulfilling the various requirements of diverse electronics or photonics thanks to their potentials for fabricating heterostructures with ultra-sharp van der Waals interfaces, which are prerequisites factors for high performance electronics fabrication [29, 30]. Recently, in several reports, the performance of discrete device based on 2D materials obtained has surpassed that of incumbent Si transistor that has dominated the semiconductor industry long since. Whereas, these devices that show the most cutting-edge performances are generously fabricated by 2D materials exfoliated from the bulk materials, which are of high quality but are restricted in lateral sizes, hindering their application potentials in constituting large scale 2D circuits to be commercialized in semiconductor industry [31, 32]. For another, innovative device structures based on 2D materials

that are capable of reducing power dissipation via overthrow-

ing the "Boltzman Tyranny" (The phenomenon that the SS

of traditional FET cannot be smaller than 60 mV dec<sup>-1</sup> stem-

ming from carrier injection transport mechanism) to make

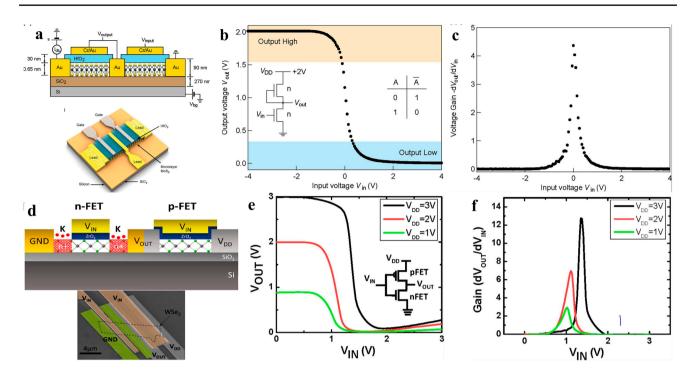

3D monolithic integration of 2D electronics, offering new

it possible to attain sufficient  $I_{on}$  with lower supply voltage are yet to be optimized [33, 34]. These post Moore's 2D materials-based ingenious device structures encompass 2D materials-based negative capacitance field effect transistor (NCFET), tunnel field effect transistor (TFET), dirac source FET (DSFET), spin transport FET (S-FET) and impact-ionization (avalenche breakdown) FET (I-IFET), which are capable of obtaining ultra-steep switching behaviors and reducing SS below 60 mV dec<sup>-1</sup>, resulting in diminished supplied voltage required [35-39]. Apart from adopting new physical mechanisms to reduce  $V_{dd}$  for the purpose of lowing down the power dissipation, making full use of the vertical direction to fabricate 3D or vertical device structures is another effective gateway to concurrently achieve sufficient gate controllability to combat with SCEs and reduce leakage current to decrement power consumption. Fin field effect transistor (FinFET) based on Si has proved itself to be deserved the honor and successfully sustain the technology node to 3 nm, though at which SCEs degradation and leakage current increment come back at the revenge [40]. In this context, nanosheet or nanowire Gate all Around FET (NS/NW GAAFET) structures that are treated to possess the ultimate gate controllability arising from the channel being surrounded by gates have come to the rescue, which are projected to further revive the Moore's law and sustain the technology to sub-1 nm node [41]. Sparked by the ingenious 3D device structures and the SCEs immunity capabilities of 2D materials, 2D materialsbased FinFET or NS GAAFET structures have been put forward and fabricated, from which promising performances have been achieved, showcasing the substantial compatibility of 2D materials with modern semiconductor production line [42-44]. More than Moore's poses the requirements of multi-functions achieved in one single chip, which can be well fulfilled by 2D materials ascribed to the feasibility of 3D integration of 2D materials-based electronics, both with Si or pure 2D circuits. 2D materials-based sensors, memristor, memtransistor, flexible transistors and radio frequency

(RF) electronics can be fused into the computing circuits fabricated with Si or 2D materials to facilitate the boosting of multi-functions to fulfill the diverse demands of modern life thanks to the compatibility of 2D materials with BEOL process of modern semiconductor industry and capability of opportunities to cram more functional circuits into one chip [45, 46]. Modern life and ICs pose urgent requirements for faster speed, lower cost, and less power consumption day by day, which lay formidable roadblocks for traditional von Neumann structure where larger latency and power consumption have been wasted in shuttling data back and forth from memory region to computing region, that is the notorious "Memory Wall", which can be ultimately addressed with Non von Neumann structure where computing is conducted in memory regions. 2D materials-based in-memory computing circuits bode well for reducing power consumption, cost and enhancing operating speed with regards to those based on traditional bulk semiconductors [46]. With numerous efforts have been dedicated to the semi-

conductor technology based on 2D materials, simple logic circuits have sprung up nowadays which showcase superior merits over traditional bulk Si based circuits in footprint reduction, multi-functions obtainment with reduced electronics counts and power consumption. Simple logic circuits based on 2D materials like inverters, NAND, NOR, OR, ring oscillator (RO), static random access memory (SRAM), or amplifiers all have been achieved up to now, which manifested the merits of proper logic functions, power consumption reduction, multi-outputs originating from the ready tunability of electronics states of 2D materials and what is more, the feasibility to reduce electronic device counts by virtue of multi-input ports of 2D materials with double channels [47-51]. Intriguingly, integrated circuits based on 2D materials that encompass divergent functions in one chip have come into view recently thanks to the inexhaustible endeavors dedicated by researchers all over the world, shedding light on the bright future of 2D materials being fused into semiconductor industry. 3D integration of 2D materialsbased electronics and simple circuits purely or with mature Si ICs also cast new light on the further miniaturization for More Moore' or diverse electronic functions incorporation for More than Moore's in IC technology [52, 53]. Albeit promising as the achievements seems, there are enormous challenges and restrictions for 2D materials-based circuits to be commercially produced some day in the future. Hitherto, most of the 2D materials-based circuits reported are single logic gates, or more complicated, several logic gates being repeated in large arrays, the research works about completed and sophisticated microprocessors or full functional integrated circuits are rare at the moment [54, 55]. The functions of the limited works about the completed circuits are far underperforming than those of Si-based ICs, let alone the low yield, disillusionary operation retention time and poor stability of the circuits. Of course, all these obstacles and challenges are ascribed to 2D materials-based circuits being in the nascent stage, which are common for all the new semiconductor materials who are about to step onto the history stage of the semiconductor industry.

This review briefly outlines the inevitable trend of 2D materials being treated as the most potential candidates in future VLSI from below several aspects. Firstly, a comprehensive introduction part give the readers the impression that the further sustainability of modern IC calls for new kinds of novel materials to succeed or complement bulk semiconductors, and fortunately, 2D materials come to the rescue just at the right time; the second part introduces the 2D materials in detail, covering the main 2D materials families according to their electronic or photonic properties; the third part summarizes several main electronic devices based on 2D materials, comprising of their physical mechanisms and current cutting-edge breakthroughs both from more Moore and More than Moore regimes; the fourth part give a brief introduction of modern IC based on 2D materials achieved by researchers both from academia and industry, covering from discrete basic cornerstone inverters, small-scale logic circuits, to large-scale full functional circuits; the final part summarized the challenges and opportunities encountered by 2D materials to be incorporated into the modern IC as a successor or complementary counterpart to bulk semiconductors, the challenges include materials synthesis, discrete device performance boosting, yield improvement and variations decrement of large scale device arrays in IC based on 2D materials. Of course opportunities and hopes exist, blossoming ICs both of more Moore and more than Moore's based on 2D materials which are characterized by ultra-high operating speed, ultra-low power consumption, substantially decreased cost and diverse functions that fulfill the envisions of future life are awaiting somewhere in the future not that far away as soon as the challenges mentioned above are conquered.

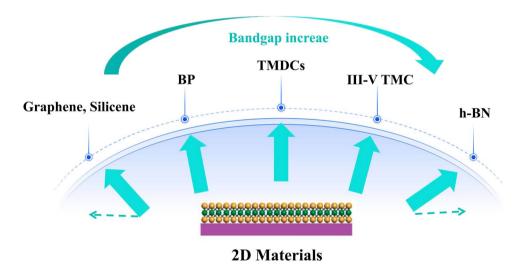

## **2** Two-Dimensional Materials

2D materials have spawn dramatic interests recently attributed to their marvelous electronic properties and a wide range of materials properties covering from insulator, semiconductor to metal which are readily to fabricate various kinds of van der Waals interfaces for different electronic or photonic purposes [56, 57]. Hitherto, there are several kinds of 2D materials that have been experimentally demonstrated, which are mainly classified into below several family groups who possess their own unique properties: (1) transition metal dichalcogenides (TMDCs), (2) black phosphorus (BP), (3) hexagonal boron nitride (h-BN), (4) mono-element compounds (Xenes), (5) III-IV Transition Metal Chalcogenide and the like. New kinds of 2D materials keeps on emerging thanks to the relentless efforts devoted by researchers both from simulation and experimental regimes, offering a plethora of platforms for various kinds of electronics or photonics [17, 58, 59].

#### 2.1 Transition Metal Dichalcogenides

TMDCs are a group of materials which are intensively studied and demonstrate paramount promises in the regimes of electronics, photonics, sensors and artificial intelligence which have attracted immense interests by virtue of their atomically thin thickness, varying bandgaps between 1 and 2 eV, which can fulfill the requirements of various applications, dangling-bonds free surfaces and relatively larger effective carrier masses that can contribute to leakage current suppression [60].  $MoS_2$  is the most representative 2D TMDC material whose monolayer form was firstly exfoliated in 1966 by Frindt with scotch tape [61], and was chemically exfoliated 20 years later [62]. Monolayer MoS<sub>2</sub> has a direct bandgap of 1.8 eV, and gradually reduces to an indirect bandgap of 0.4 eV as when it is in bulk form. Thanks to its environmental stability, 2D MoS<sub>2</sub> has been treated as the most potential supersedure or complement to 3D Si in the post Moore's era and widely investigated by researchers both from academia and industry. In the typical crystal structure of monolayer 2D MoS<sub>2</sub>, a molybdenum atom lies between two sulfide atoms, jointed together via covalent bonds, constituting a monolayer of 6.5 A. Whereas, different MoS<sub>2</sub> layers are jointed by van der Waals force, which bodes well for its monolayer 2D form to be exfoliated mechanically or chemically [63]. The burgeoning achievements and bright foreground brought about by 2D MoS<sub>2</sub> ignite immense interests in delving into 2D TMDCs materials manifested by a formula of MX<sub>2</sub>, where M stands for transition metal (for example, Mo, W, Re or Ta) who locates between two X atoms which is on behalf of the chalcogen family element (taking S, Se, Te, and O as examples), jointed by covalent bonds. Just like their counterpart MoS<sub>2</sub>, other 2D TMDCs materials are characterized of direct bandgaps in monolayer, which gradually decrease and change to indirect bandgaps with increasing thickness [64-66]. Attributed to their tunable bandgaps in a reasonable range and relatively large effective carrier mass, 2D TMDCs materials are generally hailed as suitable channel materials in electronics or photonics. In 2011, monolayer MoS<sub>2</sub> was firstly used in a transistor as a channel materials with carbon nanotube as gate, high on/off ratio of exceeding  $10^8$ , high mobility of  $200 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  and near ideal SS of 74 mV dec<sup>-1</sup> had been obtained, perfectly approaching the ideal 60 mV  $dec^{-1}$  limit for conventional transistor at room temperature, boasting their feasibility in suppressing short channel effects deriving from 2D materials' ultimate thickness [67]. From then on, tremendous efforts have been dedicated to this research regimes and various stable 2D TMDCs materials have been experimentally substantiated which cover wide range of electronic properties from semiconductor, semimetal, insulator to superconductors attributed to their crystal structures or different constituting M or X elements [65]. The most prevalent 2D TMDC materials that are used as channel materials can be categorized as n type semiconductors as MoS<sub>2</sub>, MoSe<sub>2</sub>, or WS<sub>2</sub>, p type semiconductors like MoTe<sub>2</sub> and WSe<sub>2</sub> who can demonstrates ambipolar transport behavior stemming from its specific band structure [68–70]. Crystal structures have the last words for the electronic properties of specific 2D TMDC materials, which commonly comprise of 2H, 1 T, 1 T' phase structures depending on their fabrication conditions. 2H phase TMDC materials own the crystal structure of trigonal prismatic, demonstrating semiconductor behavior, while 1 T or 1 T' phases manifest metallic behavior, offering an additional knob for phase engineering to reduce contact in 2D TMDC materials based electronics [71, 72].

The merits of 2D TMDC semiconductors to be used as channel materials in post Moore' regime lies in their carrier mobility maintenance as thickness reduces to sub-1 nm, which has been plaguing 3D semiconductors whose carrier mobility degrades substantially following the six power law as thickness reduce down to below 5 nm [73]. The reported carrier mobility of 2D TMDC materials lies around 200 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, which is consistent with that of bulk Si, holding colossal promises to be applied in Si based semiconductor industry. Nevertheless, the carrier mobility of 2D TMDC

materials can be seriously affected by interface materials and quality, thus carrier mobility of monolayer 2D TMDC materials is often significantly degraded than their multilayer or bulk forms attributed to the fact that monolayer 2D materials are more susceptible to interface states due to their ultimate thickness [74]. Encapsulation by h-BN or inserting other buffer layer or introducing strain in 2D TMDC materials is capable to help to reduce the impact of interface states and increase their carrier mobility. Newly found 2D TMDC materials of ReS<sub>2</sub>, NbSe<sub>2</sub> or TaS<sub>2</sub> show superior semiconductor or superconductor behaviors, offering additional platforms for 2D TMDC materials to be used in fundamental research or new kinds of functional devices.

#### 2.2 Black Phosphorus

Black phosphorus (BP) is a typical p type 2D semiconductor with a direct bandgap varying from 0.3 to 2.0 eV as its thickness reduces from bulk to monolayer. In BP crystals, each phosphorus atom is covalently bonded via  $sp^3$ hybridization to three neighbor phosphorus atoms, forming an orthorhombic crystal structure, leading to its semiconductor behavior while different BP layers are jointed by van der Waals force [75]. The crystal structures in x and y directions are also asymmetric, leading to different carrier mobility along armchair and zigzag directions. Albeit it is unstable in atmosphere, its high carrier mobility (over  $1000 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  in monolayer at room temperature and more than 70,000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in bulk form) still wins itself enormous trials to be used in electronics or photonics [76]. 2D BP materials are potential candidates in high performance logic electronics ascribed to their high carrier mobility and relatively modest bandgaps. A plethora of reported transistors with recorded high on state current and transconductance are made from BP materials [77–79]. Besides, thanks to their readily tunable direct bandgaps and high carrier mobility, 2D BP materials show tremendous potentials in photonics or detectors [80-82]. The prominent roadblock confronted by 2D BP materials to be applied in high performance electronics or photonics is their environmental instability, which endows enormous challenges in fabricating 2D BP based devices stemming from their rapid degradation in environment. Encapsulation via h-BN, oxide materials, or fabricating 2D BP-based devices in vacuum atmosphere or glove box can alleviate the hurdle to some extent, whereas, radical avenues should be opened up to surmount the challenges ultimately [83, 84]. For another, the readily tunable direct bandgap of BP also provides an additional knob in forming homojunctions that can contribute to sharp and ultra-clean junctions in tunnel field effect transistor, leading to boosted  $I_{on}$  without compromising steep switch behavior [85].

#### 2.3 III-IV Transition Metal Chalcogenide

III-V transition metal chalcogenides which are manifested by MX or MX<sub>2</sub> (M possesses the elements of gallium (Ga), indium (In), tin (Sn), thallium (Tl), lead (Pb), and bismuth (Bi)) and X comprises of S, Se, Te, and O) are newly emerging transition metal chalcogenide 2D materials, among which Bi-based 2D chalcogenide materials often behave as topological insulator, while Pb- or Tl-based chalcogenide materials demonstrate as three components, which are rarely considered to be used in semiconductor industry [86]. Ga-based chalcogenides materials comprising of GaS, GaSe, GaTe demonstrate relatively different properties in contrast to 2D TMDC materials, which are manifested by larger bandgaps, with bulk materials possessing bandgaps ranging from 1.7 to 2.5 eV and monolayer demonstrating bandgaps varying from 3.3 to 3.4 eV [87]. The relatively large bandgaps of Ga-based chalcogenides materials offer potential opportunities in being used in optoelectronics working in UV to visible spectrum range. For another, 2D Gabased chalcogenides materials possess unusual band alignments, resulting in larger effective carrier mass, which contributes to leakage current suppression in ultrascaled field effect transistors. Unfortunately, attributing to their larger bandgaps and effective carrier mass, carrier mobility is constrained, which lays aside substantial challenges for 2D Ga-based chalcogenides materials to be applied in high speed electronics [88]. Recently, 2D InSe material triggers enormous attentions arising from its high carrier mobility and light effective mass  $(\sim 0.14 \text{ m}_0)$ . A record high electron mobility exceeding  $3700 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  had been obtained in InSe-based FET [89], which gained to  $10^4$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in Hall structure via encapsulated by BN and contacted by graphene at liquid-helium temperature [90]. A ballistic 2D transistor with 10 nm channel length made from exfoliated InSe had been reported, the transistor exhibited a record high  $I_{on}$  of more than 1 mA  $\mu$ m<sup>-1</sup>, an ohmic contact of 62  $\Omega \mu$ m<sup>-1</sup>, SS of 76 mV dec<sup>-1</sup> and  $I_{on}/I_{off}$  ratio over 10<sup>8</sup>, a DIBL of 22 mV V<sup>-1</sup>, indicating perfectly suppressed SCEs [31]. The high mobility and relatively modest bandgap of 1.2 eV make InSe to bode well for high performance logic electronics.

Aside from group III element, group IV element as Snbased chalcogenide 2D materials have ignited immense attentions thanks to their marvelous properties. SnSe is treated as conspicuous candidate for thermoelectrics attributed to its ultra-low lattice thermal conductivity and high thermalelectric figure of merit [91]. By virtue of its low bandgap of 0.86 eV and small effective carrier mass (0.14 m<sub>0</sub> and 0.08 m<sub>0</sub> for zigzag and armchair direction), 2D SnSe materials show promise in high speed electronics. A best reported 2D SnSe-based transistor demonstrated a high electron mobility of more than  $250 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , and a on state current of 0.3 mA  $\mu \text{m}^{-1}$ with a superior on/off ratio of more than  $10^7$ , providing an additional platform for high speed electronics except for 2D BP, while getting rid of environmental instability issue at the same time since SnSe-based transistor was reported to be capable of maintaining its performance for more than three months, which had been plaguing 2D BP long since [92].

#### 2.4 h-BN and Other 2D Insulator Materials

2D materials-based electronics have been confronted with the challenges of high  $\kappa$  material integration, which has been alleviated more or less thanks to the emerging and incorporation of 2D dielectrics. Hexagonal boron nitride (h-BN) is widely studied and mostly representative 2D dielectric material with a relatively large bandgap of 6 eV and dielectric constant of ~ 5. The crystal structure of h-BN is characterized by hexagonally linked sp<sup>2</sup> hybridized B-N bonds, h-BN is capable of constituting ultra-clean van der Waals interface with 2D semiconductor channel, which is beneficial for leakage current suppression and switching speed improvement, whereas, the low dielectric constant of h-BN hampers its capability to be reduced to sub-1 nm equivalent oxide thickness (EOT), preventing it from being used in ultra-scaled electronic devices [93]. An alternative pathway is to adopt h-BN in combined with other high k dielectric materials as

HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> or ZrO<sub>2</sub>, where h-BN behaves as an interlayer which helps to reduce the interface states between 3D high  $\kappa$  dielectrics and 2D semiconductor channels [94]. Generally, the combined h-BN/high k oxide dielectrics attest to outperform pure high k oxide layer on 2D semiconductor channel. For another, ascribed to its robust environmental stability and marvelous flexibility, h-BN is prevalently used as encapsulation materials for 2D materials-based electronics, especially those who are sensitive to oxygen or moisture in atmosphere, such as BP, InSe, or MoTe<sub>2</sub> [95]. 2D materials as graphene or MoS2 encapsulated with h-BN proved to be feasible to enhance their carrier mobility substantially, the reason lies in the merits of mechanical flexibility and scalability of h-BN contributes to the scattering suppression from substrates [96]. h-BN can also serve as interlayer between 2D source/drain materials and 3D metal layer, contributing to unpinning Fermi-Level and impeding metal induced gap states (MIGS), suppressing trap states and avoiding interdiffusion between contact metal and 2D materials, promising achievements have been demonstrated which consolidate the efficacy of h-BN in helping to reduce contact resistance in 2D materials-based electronics [97].

Whist 2D h-BN possesses the feasibility of forming ultraclean interfaces between dielectric materials and 2D channels, its low permittivity limits its application in ultra-scaled electronic devices. Thus pursuing for 2D dielectric materials with high dielectric constants is imperative for 2D material based electronics to achieve high performance. Fortunately, hard work pays off ultimately. Recently, 2D van der Waals or quasi 2D van der Waals dielectrics keeps on coming into our view in the regime of 2D materials-based electronics, among which Bi<sub>2</sub>SeO<sub>5</sub> and SrTiO<sub>3</sub> are the most promising candidates [98, 99]. Bi<sub>2</sub>SeO<sub>5</sub> is generally obtained by layer by layer oxidation of Bi<sub>2</sub>O<sub>2</sub>Se, which is a newly fabricated 2D material with high mobility. Deriving from the feasibility of gradually transition of 2D Bi<sub>2</sub>O<sub>2</sub>Se semiconductor material to 2D Bi<sub>2</sub>SeO<sub>5</sub> insulator who possesses high dielectric constant of 21, transistors based on 2D Bi<sub>2</sub>O<sub>2</sub>Se as semiconductor channel and its corresponding high k native oxide 2D Bi<sub>2</sub>SeO<sub>5</sub> as gate dielectrics are promising in achieving high performance by virtue of the ultra-sharp and clean interface between channel and dielectric layer, impeding the interface trap states that can lead to high leakage current and degraded switching behavior. A field effect transistor based on such a material system demonstrated mobility higher than 300 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, on/off ratio over 10<sup>5</sup> and low

SS of ~75 mV dec<sup>-1</sup> at room temperature attributed to the ultra-clean interface between 2D channel and gate dielectric layer, based on which inverters circuits showcased voltage gain as high as 150 [100].

#### 2.5 Graphene, Germanene and Silicene

Graphene was firstly mechanically exfoliated with scotch tape in 2004 by Novoselov and Geim [14]. The emerging of graphene has opened up a new materials platform for both fundamental research and novel electronic or photonic devices, since when diverse 2D materials keep on blossoming and burgeoning with marvelous achievements having been attained. Graphene is a metallic 2D material with carbon elements arranged in a hexagonal structure, which contributes to its novel dirac cone band alignment and environmental stability, making it a super candidate for electrode in various kinds of devices [101]. The carrier mobility in graphene is high, over  $10^4$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at environment and can reach 10<sup>5</sup> when suspended [102]. Albeit the carrier mobility in graphene is extremely high, the absence of bandgap prevents graphene from being used in logic devices, which raises a claim for at least 500 mV bandgap to obtain an on/ off ratio at any rate over 10<sup>4</sup>-10<sup>7</sup> to circumvent code ambiguity [103]. Narrowing nanoribbon width provides additional knob to open a bandgap in graphene and transistors based on nanoribbon graphenes have been reported more or less, whereas, narrowing the width of graphene nanoribbon has been faced with massive challenges which encompass both experimental technique limitations and electronic properties degradation [104]. Thus graphene steers its wheel and finds ample scope for its skills that is radio frequency (RF) devices that have no requirements for bandgaps in achieving high cutoff frequency. Graphene-based RF devices demonstrates a high cutoff frequency of hundreds of GHz, only that the oscillation frequency which is key in circuit application remains low, which puts constraints on the application of graphene [105]. Besides, attributed to its superior conductivity and flexibility, graphene has been widely used as electrodes materials in both 2D materials-based electronics and photonics, where the ultra-clean van der Waals interfaces benefit for the alleviation of Fermi level pinning issues in contacts regions [101].

Silicene and germanene are allotropes of the modern semiconductor backbones of silicon and germanium, which also feature hexagonal honeycomb crystal structures alike that of graphene. Different from the fact that A and B sublattice locates in the same plane, the sublattices in silicene and germanene have a perpendicular angle to the plane, which contributes to a minor bandgap of 1.55 and 23.9 meV in silicene and germanene, shedding lights on their usages in digital logics [106]. For another, the asymmetric crystal structures also offer more opportunities for silicene and germanene to further enlarge their bandgaps via strain, applying vertical electric field or adopting other avenues [107]. The high theoretically predicated mobility of  $10^4$ – $10^5$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, feasibility in further tuning bandgaps and being allotropes of backbone channel materials of silicon and germanium make the two 2D silicene and germanene attractive to researchers in spite of their instability and huge challenges in materials synthesis. Simply put, 2D silicene and germanene are promising candidates for high performance logic electronics thanks to their high carrier mobility despite of the pronounced hurdles lay in front of the massive production of relevant electronics made from them.

# 3 Electronics Based on Two-Dimensional Materials

With the incessant downscaling of electronics, traditional 3D semiconductors have encountered paramount physical limitations in further scaling down channel thickness to fulfill the requirements of enough gate electrostatic controllability to hinder the increasingly degraded SCEs and worsen leakage currents. The emerging of various 2D materials opens up new avenues for further miniaturization of electronic dimensions deriving from the feasibility of 2D materials in maintaining high carrier mobility with channel thickness thinning down [32]. With numerous endeavors being devoted to the investigation of 2D materials, a myriad of achievements have been achieved in the regime of 2D materials-based electronics, comprising of electronics both from More Moore's and More than More's regimes [108], which will be comprehensively discussed in the below sections to give readers a holistic impressions.

#### 3.1 Electronics for More Moore's

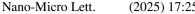

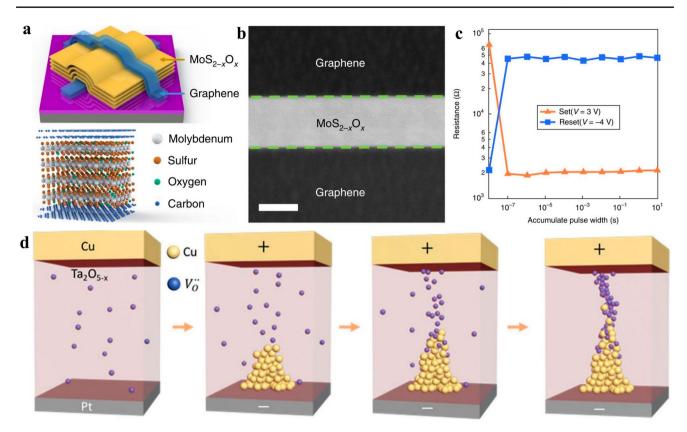

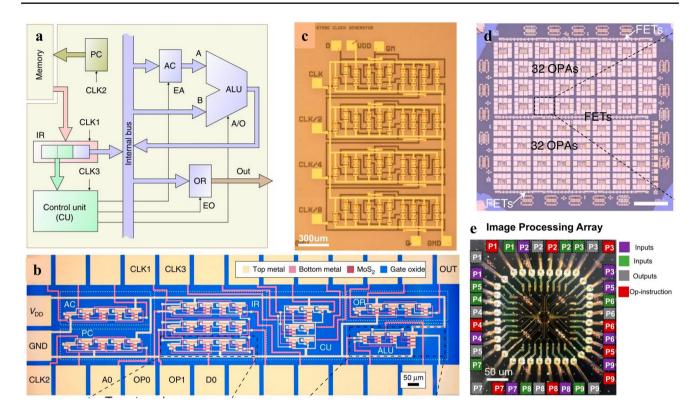

More Moore's regime denotes the era when traditional electronics encounters plateau in its scaling trend, which needs to be surmounted via adopting new materials or steering to novel device structures. The electronics in More Moore's regime are characterized by enhanced device performance in the context of marginal power consumption, which encompass logic devices and memory devices as well. In logic devices, in order to improve computing speed with dimension downscaling, electronics with new working mechanism, new channel materials or new device structures are desperate for transformative breakthroughs to combat the increasingly degraded SCEs and leakage currents. 2D materials-based electronics of new mechanism comprise of steep slope transistors as 2D materials-based tunnel field effect transistor (TFET), negative capacitance field effect transistor (NCFET), dirac source field effect transistor (DSFET), spintronic field effect transistor (S-FET), ionic impact field effect transistor (I-IFET) as mentioned above. New channel materials mainly focus on 2D materials and carbon nanotubes which stand out among many candidates attributed to their superior device performance and lower power consumption; For another, 2D materials combined with the incumbent prevalently SCEs suppression device structures as FinFET and GAAFET have spawned enormous interests as well. In memory device, except for reducing memory device dimensions to reduce the footprint of memory region to contribute to chip minimization, power consumption of memory devices is poised to be diminished to contribute to the overall power consumption decrement in modern IC chip. 2D material based memory devices possess the feasibility to reduce the supply voltage needed, resulting in diminished power consumption. For another, attributed to the atomic flat surface and transferability of the 2D materials, it is feasible to fabricate double or even multi-gates 2D materials-based electronics, benefiting for providing more inputs or outputs ports, contributing to electronic devices counts reduction in 2D materials-based memory modules, resulting in area-efficiency and power consumption inhibited ICs (Figs. 1 and 2).

#### 3.1.1 Computing Devices

The ceaseless miniaturization of electronics presents relentless requirements for power consumption decrement in the context that device performance keeps on elevating, posing enormous challenges to further scale down supply voltage in accordance with electronic dimensions, which are leveling off for a long period of time ascribed to the notorious "Boltzman Tyranny" in traditional transistors [109]. "Boltzman Tyranny" denotes the phenomenon that the SS of transistors is incapable of being reduced down below  $60 \text{ mV} \text{ dec}^{-1}$ at room temperature stemming from the carrier injection mechanism, which prevents V<sub>DD</sub> in traditional transistors from being further scaled down, hindering the reduction of power dissipation. Fortunately, the new kinds of electronics FET devices incorporating of TFET, NCFET, DSFET, and I-IFET can fulfill the demands of reducing  $V_{DD}$  without trading off device performance via ultra-steep switching phenomena, that is, SS below 60 mV dec<sup>-1</sup> [110]. What is more, the combination of steep slope FET with novel 2D materials has opened up new avenue for overcoming the fundamental limits of traditional 3D semiconductors based steep slope FETs and expediting commercialization of 2D materialsbased electronics [33].

**3.1.1.1 2D TFET** TFET has undergone a long history, whereas, during which TFETs has been plagued by low on state current ascribed to carrier transporting by band-toband tunneling (BTBT) mechanism. For another, traditional 3D semiconductors based TFET has been encountered with the hurdles of inferior interfaces laden with trap states which results in leakage current increment, intunable band diagrams, wide tunneling barriers for charge carriers, all of which contribute to  $I_{on}$  inferiority in TFET, which is several orders of magnitude smaller than that of traditional MOS-FET, posing insurmountable obstacles for 3D semiconductors-based TFETs to be commercialized [111].

The  $I_{on}$  in TFET is dominantly determined by the tunneling probability of charge carriers, which can be described as  $T_{WKB}$ . The BTBT in TFET can be comprehensively investigated via a Wentzel-Kramer-Brillouin (WKB) approach which defines the tunneling barrier as a triangular shape [112]. According to the WKB approximation, the  $T_{WKB}$ , which defines the likelihood of a charge carrier to tunnel from source to channel via transmitting through the triangular barrier, can be described as below:

$$T_{\rm WKB} \approx \exp(\frac{-4\lambda E_{\rm g}^{3/2} \sqrt{2m_{\rm t}^*}}{3q\hbar(E_{\rm g} + \Delta\phi)})$$

(1)

$m_t^*$  denotes the tunneling mass; q is the electronic charge;  $E_g$  represents the bandgap;  $\hbar$  defines the reduced Plank constant;  $\Delta \varphi$  is on behalf of the energy difference between the source valence band maxima (VBM) and channel conduction band minima (CBM);  $\lambda$  refers to the short channel screen length which is determined by the gate electrostatic controllability over channel. According to Eq. (1), a high tunneling probability,  $T_{\rm WKB}$ , which can guarantee a higher  $I_{\rm on}$ , is facilitated by a smaller tunneling mass  $m_{\rm t}^*$ , screen length  $\lambda$  and larger  $\Delta \varphi$  [113].

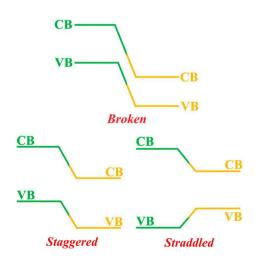

Attributed to the inferior interfaces brought about by 3D semiconductor materials, larger  $I_{on}$  with sub-60 mV dec<sup>-1</sup> SS in 3D TFET face insurmountable challenges, while fortunately, the emergence of 2D semiconductors has brought in good news for TFET structures, which have been relegated to limbo imputing their infeasibility to improve  $I_{on}$ . 2D materials cover a wide range of material types, from insulator, semiconductor to metals, which comprise of a wide range of bandgaps, holding the promise of constituting various kinds of band diagrams to provide the platform for TFET to choose the most favorable one to boost  $I_{on}$ . Three common band diagrams are generally formed between heterojunctions constituted by two different kinds of semiconductors, which comprising of staggered, broken and straddled band diagrams, among which the staggered and broken band diagrams are favorable for 2D TFETs, as shown in Fig. 3 [33]. The feasibility of constituting various homo- or heterojunctions between different 2D semiconductor materials opens up new avenues for TFET to obtain low SS and high Ion concurrently without compromising power consumption. A myriad of 2D materials-based heterojunction TFETs have been reported with sub-60 mV dec<sup>-1</sup> SS and intriguingly higher Ion that shows promise for fulfilling the requirements set by International Roadmap for Device and System (IRDS) [114–118]. To overcome the density of states (DOS) inferiority in 2D materials, some 3D semiconductors of Si, Ge or 3D BP have been chosen as source materials to constitute a 3D/2D source/channel heterojunction TFET structures, which benefit for superior Ion deriving from highly doped 3D source materials and elevated DOSs [119-121]. A relatively highly doped source with narrow bandgap and intrinsic channel with larger bandgap are preferred in 2D TFET device structure design for higher  $I_{on}$  and suppressed  $I_{\rm off}$  concurrently [121]. For another, 2D semiconductors are featured by easily tuned bandgaps via varying thickness, laying the foundation for constituting ultra-clean homojunctions via the same kinds of materials with different thickness [122, 123]. 2D TFET holds the promise of subduing the hurdles confronted by conventional 3D TFET and achieving higher I<sub>on</sub> and steep switch simultaneously, paving the way for TFET to be commercialized someday in the future.

Fig. 1 Evolving trend of Integrated Circuits with time, one is more Moore's and the other is more than Moore's, reprinted with permission from Ref. [12, 150, 194, and 256]

Fig. 2 Classifications of 2D materials, mainly comprising of metallic graphene, germanene, and silicene; BP; TMDCs; III-V TMC and insulator h-BN

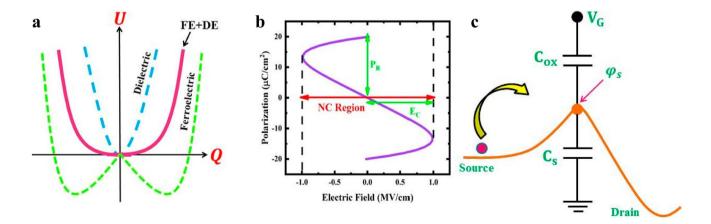

**3.1.1.2 2D** NCFET NCFET is another potential "green" transistor with steep switch behavior. By incorporating an additional ferroelectric materials layer during the fabrication of gate electrode, internal voltage amplification effect can be introduced into NCFET structure which contributes to steep switch behavior from on state to off state in NCFET with  $I_{on}$  boosted up synchronously. Different from TFET which depends on adopting new charge carrier transport mechanism to obtain sub-thermionic SS, NCFET demonstrates steep

switch phenomenon via making use of the negative capacitance effect of ferroelectric materials inserted in the gate dielectric layer to boost up charge deviation caused by voltage variation, resulting in body factor m to be smaller than 1, leading to sub-60 mV dec<sup>-1</sup> SS according to Eq. (2), where m is on behalf of the body factor that describes the charge deviation endowed by voltage changing; n is termed as the transport factor that signifies the drain current altering behavior induced by channel surface potential variation;  $\varphi_{\rm S}$  is on behalf of surface potential of the channel;  $C_{\rm S}$  manifests the capacitance of semiconductor transistor below gate oxide, while  $C_{\rm gate}$  signifies the capacitance of the gate, encompassing the combination of dielectric and ferroelectric capacitance [124];

$$SS = \frac{\partial V_G}{\partial \log_{10} I_D} = \frac{\partial V_G}{\partial \phi_S} \cdot \frac{\partial \phi_S}{\partial \log_{10} I_D} = m \cdot n$$

$$m = \frac{\partial V_G}{\partial \phi_S} = (1 + \frac{C_S}{C_{gate}})$$

$$n = \frac{\partial \phi_S}{\partial \log_{10} I_D} = \frac{k_B T}{q} \ln(10) = 60 \text{mV/dec}$$

(2)

NCFET holds the merits of compatibility with modern semiconductor manufacturing procedure, substantiated by NC-FinFET-based logic circuits demonstrated superior performance than FinFET of the same technology node, which was checked by Wei-Xiang You et al. with the aid of a shortchannel NC-FinFET compact model in 2019 [125]. Promisingly as NCFET has showcased in commercial application, hysteresis behavior poses a paramount hurdle in the application of NCFET, aside from a potential instability issue; inability to scaling down ferroelectric materials in proportional to device dimension diminishing and so forth [126]. Fortunately, the hysteresis behavior can be suppressed to a pronounced extent by capacitance matching imposed by tuning capacitance of ferroelectric materials to match well with that of the MOSFET to make sure that the ferroelectric materials work stably in negative capacitance region by confirming that the Gjbbs energy of the composite system comprising of ferroelectric material and dielectric materials possess

Fig. 3 Schematics of straddled (*type I*), staggered (*type II*) and broken (*type III*) band diagrams [33]

one lowest energy at zero voltage point, as demonstrated by Fig. 4a. The ferroelectric capacitance,  $C_{\rm fe}$  that can fulfill the expectation of hindering hysteresis behavior and minimizing SS as much as possible must meet the conditions as below according to Fig. 4c [126],  $-1 < C_S/C_{OX} < 0$ , where  $C_{OX}$  is the total capacitance of dielectric and ferroelectric materials and  $C_S$  is the capacitance of transistor and is always positive. To guarantee the NCFET to function without hysteresis and possess steep switch behavior,  $|C_{OX}|$  should be larger than  $C_S$ , and the more the  $|C_{OX}|$  is near to  $C_S$ , the smaller the SS is. Once  $|C_{OX}|$  is substantially larger than  $C_S$ , the internal voltage amplification effect gets almost smeared, resulting in negligible steep switching behavior.

NCFET can be categorized either by ferroelectric materials or via gate stack structures. Ferroelectric materials can be divided into organic, perovskite, HfO2-based and 2D ferroelectric materials, among which HfO2-based ferroelectric materials demonstrate promising potential to be used commercially attributed to the fact that HfO<sub>2</sub> is the prevalent high k oxide materials used in modern semiconductor industry, while 2D ferroelectric materials who emerged recently demonstrate potential in 2D NCFET to impede surface interface states that lead to both high leakage current and smeared steep switch behavior [127, 128]. For another, gate stacks encompass metal-ferroelectric-semiconductor (MFS), metal-ferroelectric-insulator-semiconductor (MFIS) and metal-ferroelectric-metal-insulator-semiconductor (MFMIS) structures, among which MFIS gate stack stands out deriving from both relatively simple manufacturing process and superior device performance [129].

2D NCFET combine the merits of both NCFET and 2D materials to guarantee the restless minimization of electronic devices. The commonly used ferroelectric materials in 2D NCFET encompass organic ferroelectric materials, HfO<sub>2</sub>-based ferroelectric materials and recently emerged 2D ferroelectric materials [130]. The delicate interfaces between 2D semiconductor channels and 3D ferroelectric materials often result in massive trap states that can smear out the ultra-steep switch behavior, leading to prodigious challenges in achieving sub-60 mV dec<sup>-1</sup> SS in 2D NCFET [131]. A 2D NCFET with organic ferroelectric materials poly(vinylidene difluoride-trifluoroethylene) (P(VDF-TrFE)) combined with 2D  $MoS_2$  or  $MoSe_2$  channels obtained an ultra-low SS of 24.4 mV dec<sup>-1</sup> and sub-60 mV dec<sup>-1</sup> SS over four orders of magnitudes drain current under a drain bias of 0.1 V [132]. Attributable to the prodigious potential

in commercial application of HfO<sub>2</sub>-based ferroelectric materials, 2D NCFETs based on HfO2-based ferroelectric materials have garnered monumental attentions. Mengwei Si and coworkers for the first time fabricated a 2D NCFET based on hafnium zirconium oxide (HZO) and 2D MoS<sub>2</sub> channel, a minimum SS of 5.6 mV dec<sup>-1</sup> and maximum I<sub>ds</sub> of 510 uA um<sup>-1</sup> with extraordinary on/off ratio had been attained [133]. By transferring MoS<sub>2</sub> channel on top of metal-hafnium zirconium oxide (HZO) ferroelectric-metal structure and varying ferroelectric material thickness, Felicia A. McGuire achieved a minimum SS of 6.07 mV  $dec^{-1}$  with an average SS of 8.03 mV dec<sup>-1</sup> over 4 orders of magnitude  $I_{ds}$ , a  $V_{th}$  shift in accordance with source/drain overlap capacitance and HZO or HfO2 thickness variation, demonstrating promising potential in dimensional and  $V_{\rm th}$  scaling in 2D NCFET [134]. 2D NCFET based on 3D perovskite ferroelectric material also achieved sub-60 mV  $dec^{-1}$  SS by marginally tuning 2D NCFET device structure [135]. Albeit 2D NCFETs with HfO2-based ferroelectric materials have witnessed promising achievements, the obstacles in attaining ultra-clean interfaces between 3D ferroelectric materials and 2D channels are still desperate for efforts to be devoted to by researchers to solve. In this context, the discovery of 2D ferroelectric materials is just in time, holding the promise of forming ultra-clean interfaces between ferroelectric material and 2D semiconductor channels with trap states enormously hampered [136]. CuInP<sub>2</sub>S<sub>6</sub> (CIPS) and  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> are widely used 2D ferroelectric materials in 2D NCFET [137]. Xiaowei Wang and coworkers demonstrated a 2D CIPS-based van der Waals 2D NCFET with SS below Boltzmann's limit for 7 decades of  $I_{ds}$  and minimum SS of 28 mV dec<sup>-1</sup>, where the expanded scope of I<sub>ds</sub> for sub-thermionic SS compared with 3D ferroelectric materials based 2D NCFET originated from the ultra-clean interface between 2D CIPS and below 2D semiconductor channel without dangling bonds [138]. Jiyou Jin et al. demonstrated a dual gated coupled ReS<sub>2</sub>/h-BN/ $\alpha$ -In<sub>2</sub>Se<sub>3</sub> device structure who could function as high-performance non-volatile memory, programmable rectifier, and negative capacitance field-effect transistor and a minimum SS of 24.5 mV dec<sup>-1</sup> with hysteresis free behavior when NCFET function had been spurred [139]. New kinds of 2D ferroelectric materials have been keeping on emerging in recent years thanks to the incessant endeavors dedicated by researchers, unfolding a new trajectory toward further improving the performance of 2D NCFET, providing monumental potential for 2D NCFET to be used commercially some day in the future [140].

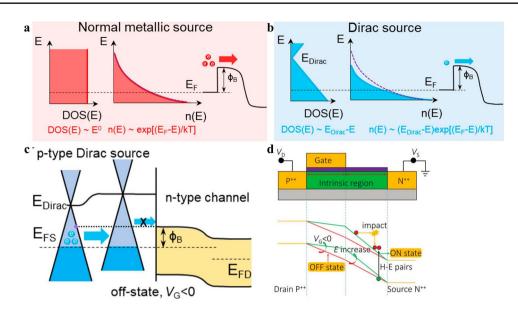

**3.1.1.3 Other Kinds of "Green" Transistors** Aside from 2D TFET and 2D NCFET that are extensively studied, other kinds of 2D materials-based transistors possess sub-thermionic SS encompass 2D DSFET, 2D S-FET or 2D I-IFET [38, 141, 142]. A 2D DSFET relies on Dirac source materials to filter out high-energy electrons to cut off the Boltzmann tail to obtain a sub-60 mV dec<sup>-1</sup> SS, as showcased in Fig. 5a [143–145]. The sub-thermionic SS in DSFET arises from the DOS in Dirac materials decreasing rapidly with energy increasing, leading to n(E) super-exponentially decreasing with energy, thus suppressing the high energy thermal tail, which is a prevalent phenomenon in normal source materials whose DOSs are constant or increase in

Fig. 4 a Free energies versus charge carriers of ferroelectric, dielectric, and ferroelectric/dielectric heterostructure; b S shaped polarization versus electric field curve of ferroelectric material; c Capacitance equivalent circuit of NCFET, the  $C_{OX}$  comprises of ferroelectric and dielectric materials [126]

accordance with the increasing of energy, resulting in the electron density to decrease sub-exponentially or exponentially with the increasing of energy [143]. Graphene is the most widely studied Dirac source material, and it is hypothesized that gapped graphene can even hinder SS to a smaller value by virtue of the bandgap further hampering the high energy electrons distribution tail, leading to DOSs and n(E)to decrease more exponentially [144]. The on state current of DSFET is dependent on thermionic injection as depicted in Eq. (3) [143], where q is the charge carrier; h is Plank's constant; T(E) describes the transmission probabilities from source to drain;  $E_{\text{Dirac}}$  denotes the energy of Dirac source material;  $\Phi_{\rm B}$  is the Schottky barrier that signifies the energy difference between the source Fermi level  $E_{FS}$  and the top of channel barrier. According to Eq. (3), SS can be smaller than 60 mV dec<sup>-1</sup> when  $\Phi_{\rm B} < E_{\rm Dirac}$ , and attributed to the fact that the thermal injection of carriers determines the on state current, 2D DSFET can circumvent the roadblock of inferior I<sub>on</sub> encountered by TFET,

whose SS was 57 mV dec<sup>-1</sup>. And intriguingly, the larger the bandgap in graphene, the smaller the SS was, which was accounted for by enhanced suppression ability over thermal distribution tail with larger bandgap [147]. With a comprehensive materials and device simulation model at atomic level, Juan Lyu et al. suggested that 2D transitionmetal dichalcogenides and 2D transition-metal carbides were rich libraries for cold sources materials attributed to their specific density of states-energy relations. According to their simulation results, pristine graphene, doped graphene, Cd<sub>3</sub>C<sub>2</sub>, T-VTe<sub>2</sub>, H-VTe<sub>2</sub>, and H-TaTe<sub>2</sub> cold sources based DSFETs with monolayer InSe as channel all could demonstrate SS below thermionic limit of 60 mV dec<sup>-1</sup>, serving as springboard for further studies to be conducted on low power consumption electronics [110]. Recently, 2D "cold" metal 2H MS<sub>2</sub> (M = Nb, Ta) is speculated to be capable of achieving sub-60 mV dec<sup>-1</sup> SS. Simulation results of cold

$$I_{\text{therm}} = \frac{2q}{h} D_0 \int_{\Phi_B}^{+\infty} dET(E) \left| E - E_{\text{Dirac}} \right| \approx \frac{2q}{h} D_0 \int_{\Phi_B}^{+\infty} dE \left| E - E_{\text{Dirac}} \right| \exp(\frac{-E}{k_B T})$$

$$\Phi_B < E_{\text{Dirac}} I_{\text{therm}} = \frac{2q}{h} D_0 k_B T \left[ 2k_B T e^{\frac{-E_{\text{Dirac}}}{k_B T}} + (E_{\text{Dirac}} - \Phi_B - k_B T) e^{\frac{-\Phi_B}{k_B T}} \right]$$

$$SS = \frac{k_B T}{q} \frac{1}{C_1} \left[ 1 - \frac{k_B T}{(E_{\text{Dirac}} - \Phi_B)} \right]$$

(3)

Ever since graphene has been used as Dirac source material in a 2D MoS<sub>2</sub> based DSFET, and an average sub-thermionic SS of 40 mV dec<sup>-1</sup> over four decades of current has been obtained with a large  $I_{60}$  of 40 µA µm<sup>-1</sup>, 2D DSFET has gone through a burgeoning and blossoming period of harvesting season, when prodigious kinds of Dirac/cold source materials have been investigated, and various kinds of novel source structures that function like cold source materials have been brought out [145, 146]. Apart from graphene, gapped graphene was consolidated to be capable of working as cold source as well by Fei Liu and coworkers. Furthermore, attributable to enhanced suppression behavior of gapped graphene over the thermal distribution tail brought about by the opened gap in graphene, a steeper switching behavior could be obtained in 2D DSFET based on gapped graphene Dirac source. An improved SS of 29 and 28 mV dec<sup>-1</sup> had been attained in 2D DSFETs with graphene possessing gaps of 100 and 200 meV than that of 2D DSFET using gapless graphene Dirac source,

metals-based MOSFETs with idealized structures demonstrated inspiring results that not only SS of such cold metals sources FETs (CM-FET) attained sub-60 mV dec<sup>-1</sup> level, but also  $I_{on}$ , cut off frequency  $f_T$  and negative differential resistance (NDR) also showcased superior results. NbS<sub>2</sub>/  $MoS_2$  CM-FET obtained a peak current of 4110  $\mu$ A  $\mu$ m<sup>-1</sup>, several orders higher than the typical tunneling diodes owing to the broken bandgap structure of NbS<sub>2</sub>/MoS<sub>2</sub> heterojunction. The largest peak-to-valley ratio of  $1.1 \times 10^6$  is obtained by  $TaS_2/MoS_2$  CM-FET with  $V_{GS}$  of -1 V at room temperature, providing practical applications for more Moore and more than Moore's developing roadmaps [148]. Aside from 2D materials, 3D cold metals can also be fused with 2D channel materials to make 2D DSFETs that are feasible of making full use of the high density of states of 3D sources and superior electrostatic controllability of 2D channels. In 2023, Ligong Zhang and coworkers checked DSFETs with six kinds of 3D cold metals as sources, which includes three sulfides and three oxides, in combined with monolayer MoS<sub>2</sub> as channel. Quantum transport modeling demonstrated that

Fig. 5 Energy vs density of states distributions of **a** normal and **b** Dirac source materials; **c** Band diagram of Graphene/MoS<sub>2</sub> DSFET at off state [150]; **d** I-IFET device structure schematic and band diagrams for p-I-IFET at on/off state respectively [33]

SS below 60 mV  $dec^{-1}$  spreading over five decades and on state current as high as  $5.7 \times 10^2 \,\mu\text{A} \,\mu\text{m}^{-1}$  could be obtained in these 3D cold sources based MoS<sub>2</sub> DSFETs, opening up new avenues for 2D DSFETs to boost Ion and offering a new territory of Dirac sources for DSFETs to fully delve into the performance potential of 2D materials-based DSFETs [149]. Other kinds of novel device structure as of GAA structure has been terrified to be capable of being combined with 2D DSFET structure to obtain steeper SS by virtue of Dirac source's filtering effect and high  $I_{on}$  deriving from boosted gate controllability brought about by GAA structure [150]. What is more, theoretically, the 2D DSFET device structures are feasible of combining with other kinds of "green" transistor mechanism to fabricate 2D DS-NCFET [151], 2D DS-TFET and moreover, holding enormous potential to further minimize transistor dimensions with power consumption suppressed and sustain Moore's law to even advanced technology node.

2D I-IFET makes full play of the famous avalanche breakdown phenomenon to achieve an abrupt off state to on state transition, resulting in an ultra-small SS. Concisely, avalanche breakdown depicts a phenomenon that an electron or hole with high kinetic energy originating from high electric field collides with lattice atom and impact its electrons or holes into free ones, and the kicked out electrons or holes further impact and ionize more free electrons or holes under the acceleration of an electric field, leading to an avalanche breakdown phenomenon and abrupt current multiplication. Attributed to the carrier multiplication effects and the abrupt and rapid function of electric field, I-IFET is characterized by high on state current and ultra-low SS, which have garnered monumental interests to I-IFET by virtue of its potential application in high performance low power consumption electronics [152]. The common structure of an I-IFET is a p-i-n or p-n diode structure, as demonstrated in Fig. 5d below, when  $V_{es} < V_t$ , the electric field is not strong enough to stimulate avalanche breakdown effect, thus the I<sub>ds</sub> is dominated by the inverse drain current of the diode, which is limited to a small value, resulting in an ultra-low leakage current. As  $V_{gs}$  increase to above  $V_p$  avalanche breakdown phenomenon takes place abruptly and violently, leading to an ultra-low SS and high Ion. Generally, in p-i-n I-IFET structure, the intrinsic region functions as a place where avalanche breakdown phenomenon takes place and tunes the length of the channel, eventually assisting in reducing bias voltage applied [142]. The 2D I-IFET combine the merits of high Ion, small leakage and ultra-low SS possessed by I-IFET and the feasibility of reducing supply voltage required to spur carriers' avalanche breakdown phenomenon, thus holding promising potential to renew ardors to 2D I-IFET to be used in low power consumption circuits [153]. Similar to 2D TFET, the fabrication process of 2D I-IFET also has been complicated by the asymmetric

source/drain doping species, and what is more, the supply voltage of 2D I-IFET is high attributable to the fact that avalanche breakdown requires high electric field to ignite, contracting to the low power consumption purpose set by modern electronics, thus a plethora of endeavors have been devoted to decrement  $V_{gs}$  required in 2D I-IFET and promising achievements have been attained [154–156]. More attempts are needed to be dedicated to further diminish the supply voltage needed to trigger avalanche breakdown in 2D I-IFET to make it more appropriate to be used in modern low power consumption electronics.

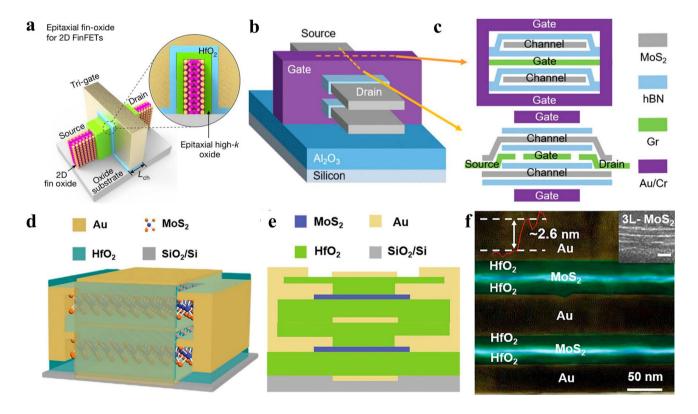

3.1.1.4 2D FinFET and 2D GAAFET The incessant miniaturization of electronic transistors has hastened parturition of 3D transistor structures, encompassing the prevalent FinFET at present stage and GAAFET structure for the upcoming technology node. FinFET structure has been adopted to ameliorate the increasingly degraded SCEs and leakage currents coming along with the scaling down of channel length in planar transistor at 21 nm technology node [40]. Encouragingly and promisingly, the increment of gate number brought in by 3D FinFET structure has enhanced gate electrostatic controllability over channel, resulting in SCEs suppression and leakage current inhibition, guaranteeing the sustainability of Moore's law further beyond 5 nm technology node [157]. The efficacy and achievements of adding gates number in suppressing SCEs and leakage current corroborated by Fin-FET structure have further incubated the GAAFET device structure, which is noted by its ultimate gate electrostatic controllability brought about by gates surrounding around the channel region. As one would expected, GAAFET structure has been proved to be more effective and testified itself to be feasible to further push the Moore's law to sub-1 nm node [158]. As a matter of course, it is natural to combine 3D device structures with 2D semiconductor channels to realize the full functions of both their merits, that is, the superior gate electrostatic controllability coming along with 3D device structures and the SCEs immunity capabilities brought along by 2D semiconductor channels. In 2014, Kausik Majumdar et al. firstly checked the ballistic performance of an TMD-based FinFET structure with an ultimate gate length of sub-5 nm with simulation method, and found that an intact electrostatic integrity still remained in TMD based FinFET transistor at such limited gate length conditions, showing pronounced potential of 2D materials-based FinFET devices for ultra-low-leakage current applications with small footprint, excellent energy efficiency, and moderate performance [159]. The next year, Min-Cheng Chen and his coworkers demonstrated a 4 nm TMD-based FinFET with back gate control for the first time, showcasing TMD could potentially provide sub-1 nm thin monolayer body for 2 nm technology node [160]. Enormous endeavors have been dedicated to fabricate 2D materials-based FinFET devices that are compatible with modern semiconductor industry fabrication process. In 2019, Yu Pan et al. presented a MoS<sub>2</sub> transistor with 10 nm gate length and p-doped Si fin as back gate electrode, which showed process compatibility with conventional Si-FinFET manufacturing process flow and marked the first time to realize large-scaled fabrication of arrayed MoS<sub>2</sub> transistors. The MoS<sub>2</sub> transistor comprised of a monolayer thin MoS<sub>2</sub> channel of 0.7 nm, exhibiting super switching characteristics and large on/off ratio of over 10<sup>6</sup>, showing great promise of incorporating ultrathin 2D materials into modern semiconductor industry [161]. In 2020, Mao-Lin Chen and coworkers fabricated a FinFET with one atomic layer fin, which was obtained by a template-growth method that fitted with different kinds of 2D crystals to isolate into monolayer in a vertical manner. The FinFET with one atomic layer thin fin presented an on/off ratios reaching 10<sup>7</sup>, shedding light on further diminishing fin width to atomic limit, holding promise to obtain electronics with larger integration density and lower power consumption [162]. In 2023, Hailing Peng and his research group members fabricated vertically aligned arrays of 2D Bi<sub>2</sub>O<sub>2</sub>Se/Bi<sub>2</sub>SeO<sub>5</sub> epitaxial fin-oxide heterostructures, as demonstrated in Fig. 6a which demonstrated high electron mobility of 270 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, ultra-low leakage current of 1 pA  $\mu$ m<sup>-1</sup>, high on/off ratio up to 10<sup>8</sup> and high on-state current of 830 µA µm<sup>-1</sup> at 400 nm channel length, opening up new avenues for further extending Moore's law. The native oxide of Bi<sub>2</sub>SeO<sub>5</sub> had been obtained by layer by layer oxidation of 2D Bi<sub>2</sub>O<sub>2</sub>Se, which provided additional knob to obtain ultra-clean interface between 2D semiconductor channels and dielectric layers, paving avenues for eschewing the massive interface states commonly existing between 2D semiconductor channels and deposited 3D dielectric layers [163].

Aside from 2D materials-based FinFET structure, recently, 2D semiconductors have also been introduced into GAAFET (termed as 2D MBCFET) device structure to harness the ultimate gate electrostatic integrity of GAA gate structure and the SCEs immunity attributes of 2D materials. In 2018, Ruiping Zhou and Joerg Appenzeller demonstrated a 3D integrated multi-channel  $MoS_2$  FET device, the  $MoS_2$ channels were surrounded by double gates and the twostacked  $MoS_2$  channels shared a common gate, which possessed the merits of super gate controllability brought in by GAA gate structure and the SCEs suppression capabilities coming along with the ultimate thickness of 2D semiconductor channels. Promisingly, the 2-stacked MoS<sub>2</sub> device showed a high on state current of 535  $\mu$ A  $\mu$ m<sup>-1</sup>, rivaling that of the recorded highest value, and an ultra-low leakage current of below 1 pA at V<sub>ds</sub> of 1 V [164]. From then on, 2D material based multi-channel stacked device structures have witnessed burgeoning developments, and thriving achievements have been obtained, all of which have showcased high driving current and lower leakage current attributed to enhanced gate electrostatic integrity and ultra-thin channel thickness [44, 165, 166]. In 2021, Peng Zhou's research group demonstrated a two-channel stacked MoS<sub>2</sub> based GAAFET structure, the MoS<sub>2</sub> channels both had thickness of 2 nm, and the normalized drive current of 23.11 µA\*µm  $\mu m^{-1}$  in each channel exceeded that of 7-level-stacked Si MBCFET, with a ultra-low leakage current of only 0.4% of that of Si MBCFET, exhibiting the superiority of 2D channel materials in superseding Si in MBCFET, unfolding a new trajectory toward further expending Moore's law [44]. In 2022, Hitesh et al. investigated a 3-level stacked MoS<sub>2</sub> based MBCFET for the first time via simulation, where each channel was double-gated. The 3-level stacked MoS<sub>2</sub> MBCFET showcased a high saturation current of 174.9 µA, with a near-ideal SS of 63 mV  $dec^{-1}$  and a high on/off ratio of over 10<sup>8</sup>, demonstrating a boosted current without compromising electrostatic control [167]. In the same year, Peng Zhou and Wenzhong Bao's research group firstly fabricated large-scale MoS<sub>2</sub>-based 2-level stacked MBCFET by virtue of 2D materials' merits of stackability, atomic thickness and marvelous electrical properties, the drive current of twolevel stacked MoS2 MBCFET could reach up to 60 µA under 1 V bias, they also came to the conclusion that 2D MBCFET possess superior carrier mobility and SS, showing potential application in future semiconductor technology node [168]. In 2023, Xiong Xiong et al. fabricated 2-monolayer-MoS<sub>2</sub>-stacked GAAFETs on large scale, where GAAFET with channel length of 100 nm demonstrated  $I_{on}$  over 400  $\mu$ A  $\mu$ m<sup>-1</sup> per channel footprint at  $V_{ds}$  of 1 V and low contact resistance of 0.77 k $\Omega$  µm<sup>-1</sup>. The performance evolution trend was testified via checking hundreds of devices with various channel lengths, demonstrating the potential of

**Fig. 6** a A Bi<sub>2</sub>O<sub>2</sub>Se/Bi<sub>2</sub>SeO<sub>5</sub> 2D FinFET device schematic [163]; b A 2-layer-stacked MoS<sub>2</sub> MBCFET schematic and **c** the detailed profiles perpendicular to and along the channel directions [44]; **d** 3D schematic and **e** cross-section schematic of a MoS<sub>2</sub> MBC-FET, **f** cross-section high-resolution transmission electron microscopy (HRTEM) image of MoS<sub>2</sub> MBC-FET [168]

monolithic integration of large-scale 2D materials thanks to their stackability and atomic thickness [169].

#### 3.1.2 Memory Devices

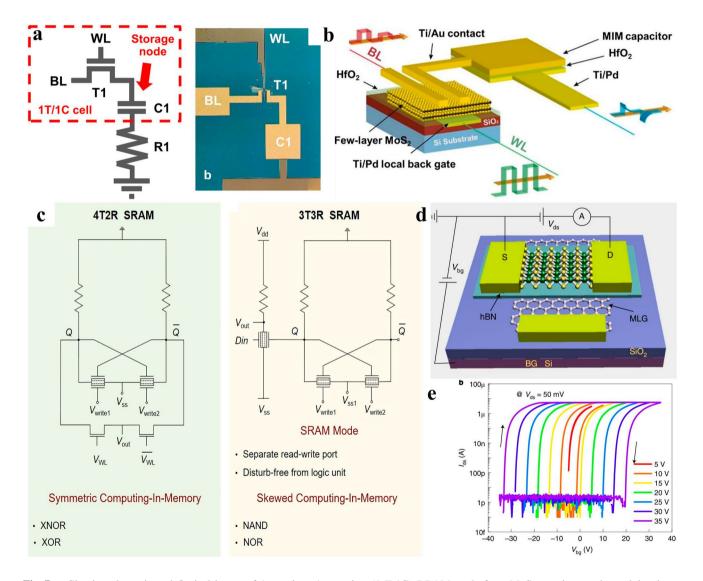

Except for logic devices, the unremitting minimization of IC requires the memory region to be reduced as well. Memory devices are categorized into volatile and non-volatile types. Volatile memories are represented by dynamic random access memory (DRAM) and static random access memory (SRAM) who are characterized by high read and write speed while constrained by lower retention time that needs to be refreshed regularly by external power supply, resulting in a waste of energy. Non-volatile memories mainly comprises of flash, phase change memory (PCM), and ferroelectric resistor access memory (FRAM) who take the advantages of long retention time (longer than 10 years) even without power supply while suffer from lower data extracting speed, which limits their applications in computing process unit while can serve as movable disks that are indispensable in modern life. The relentless minimization of IC also set constraints and challenges for memory devices, that is, more dense, higher speed, longer retention time, and less power consumption concurrently. Thanks to their ultimate atomic thickness, 2D materials outperforms traditional 3D semiconductors in feasibility to reduce supply voltage to reduce power consumption effectively. On the other hand, the super stackability of 2D materials casts a new light on obtaining more inputs or outputs terminals in one single devices by leveraging the double surface of 2D materials, offering the opportunities to reduce device numbers in memory modules, thus reducing power consumption and footprint concurrently. The leakage current suppression ability of 2D materials ascribed to their ultimate thickness contributes to power consumption reduction. Thorough discussions of 2D materials-based volatile memories of DRAM, SRAM and typical non-volatile memory of flash have been comprehensively discussed below to give readers concise impression on 2D memory devices, and the non-volatile memories of PCM, FRAM which hinged on specific materials will be discussed in forthcoming work which specifies on memory device summary later.

**3.1.2.1 2D DRAM** DRAM is featured by a capacitor in combined with a transistor that contribute to footprint reduction, where the logic signal is stored in the capacitor, whose

high speed of charging and discharging contributes to high read and write speed of DRAM while needs to be refreshed regularly by external supply power, resulting in power dissipation increment. As the semiconductor technology node evolves, the increasingly degraded SCEs brought about by device dimension down-scaling lead to leakage current increment, which is imperative to be addressed promptly by steering to new materials that are immunity to SCEs and capable of inhibiting leakage current. 2D materials are famed for their capabilities to counter SCEs and impeding leakage current attributed to their ultimate thickness, thus 2D materials-based DRAMs have engendered marvelous interest [170]. Among the many 2D materials, 2D TMDCs are widely considered as potential candidates to supersede or complement 3D Si in the future semiconductor industry, the ultra-low leakage current obtained in 2D TMDCs based MOSFETs has motivated the researchers to fuse them in DRAMs which mainly pay attention to transistor's leakage current suppression ability. Chaitanya U. Kshirsagar et al. firstly fused a MoS<sub>2</sub> 2D FET in a DRAM structure to leverage its ultra-low leakage current stemmed from the high bandgap of 1.8 eV in monolayer MoS<sub>2</sub>, which gave rise to leakage current as low as ~1 fA in DRAM circuits. For another, the retention time for 1 T/1C and 2 T gain cell memory devices reached as high as 0.25 and 1.3 s, showing dramatic potential in power consumption reduction [171]. Yin Wang et al. demonstrated a 2-transistor-1-capacitor (2 T-1C) configuration in 2021 based on monolayer MoS<sub>2</sub> transistor and a metal-insulator-metal (MIM) capacitor, where 1 T-1C configuration functioned as a DRAM memory region while another transistor acted as the computing region. The 2 T-1C configuration demonstrated a multilevel voltage stages on the capacitor and long retention time thanks to the ultra-low leakage current of MoS<sub>2</sub> transistor. They found that this 2 T-1C unit incorporating of computing and memory regions concurrently could function as a small in-memory computing circuit, offering potential opportunities to be integrated into future 3D dense lower power consumption circuits [172]. Using Monte Carlo simulation method, Mahdiye Raoofi and Morteza Gholipour compared a 2D TMDFET based DRAM with a Si-MOSFET based DRAM at the 16 nm technology node with fair conditions for different technologies, by evaluating the different performance of a digital circuits, they drew the conclusion that TMDFET-based DRAM consumed overall high power and demonstrated high variability than Si-MOSFET-based DRAM, whereas, TMDFET-based DRAM had higher timing characteristics [173]. In all, the overall researches about 2D DRAM manifested inspiring results, further endeavors are waited to be dedicated to the evaluation of their performance and limitations to further consider their value in lower power dense circuit application.